# Ceramic capacitor technology

CeraLink® opens new dimensions in power electronics

#### **TDK Electronics AG**

# CeraLink in a shot - optimized for conditions under operation in power electronics

#### Use CeraLink when

- Space requirement is tight

- Temperature is demanding (+150 °C)

- High current rating is vital

- Requirements for capacitance density are tough

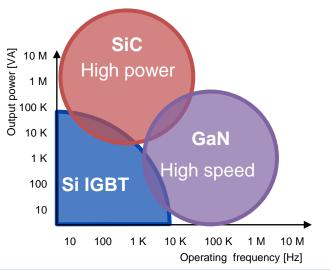

- High switching frequencies are applied (SiC, GaN)

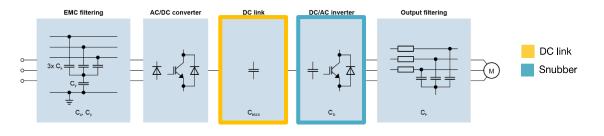

#### Main function in HV application

- Snubber capacitor

- Filter capacitor

- Flying capacitor

- DC-Link capacitor

#### CeraLink technology supports

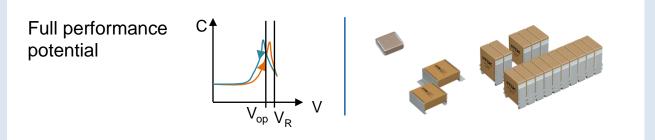

- Increasing capacitance with DC bias and best in class capacitance density at operating point (V<sub>op</sub> + T<sub>op</sub>)

- High current capability due to low losses at high frequencies (up to several MHz) and high temperatures (up to +150 °C)

- No limitation of dV/dt

- Good self-regulating properties

- Qualification based on AEC-Q200 rev. D

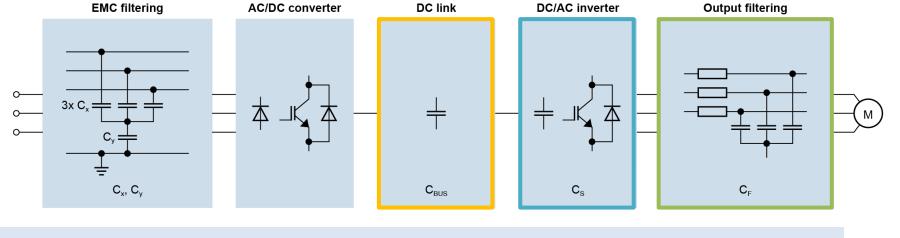

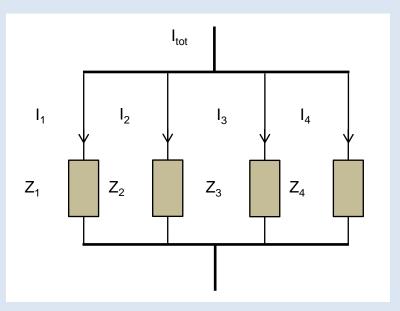

Principle circuit diagram of function of capacitors in e.g. motor drives

| Measurement condition                                                       | Film<br>capacitor      | MLCC<br>class II       | CeraLink   |

|-----------------------------------------------------------------------------|------------------------|------------------------|------------|

| Typical capacitance density  @ DC link voltage, 20 V <sub>RMS</sub> , 25 °C | 0.7 μF/cm <sup>3</sup> | 2.5 µF/cm <sup>3</sup> | 4.9 µF/cm³ |

| Typical current rating per capacitance @ 100 kHz, 105 °C                    | < 1 A/µF               | < 4.5 A/μF             | 11 A/μF    |

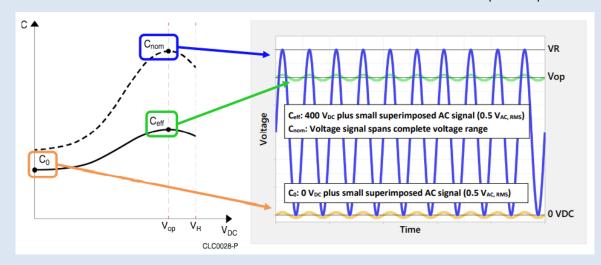

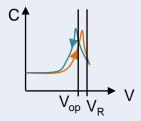

# CeraLink's special behaviour 1

### Some differences to MLCC

| Linear       | Ferroelectric | Antiferroelectric |

|--------------|---------------|-------------------|

| MLCC class I | MLCC class II | CeraLink          |

| μF           | μF            | μF                |

| V            | V             | V                 |

### Feature: Positive bias behaviour

- Increasing capacitance with DC bias between 0 V and V<sub>op</sub>

- Best in class capacitance density at operating point (V<sub>op</sub> & T<sub>op</sub>)

More to this in the CeraLink

Technical Guide

# CeraLink's special behaviour 2

### At high temperature

- Operating temperature up to +150 °C

- Low losses at high temperature

- Low leakage current

- No thermal runaway

- Generally low self-heating AND self-heating supports

CeraLink to come to temperature for good performance

### At high frequency

- Optimal frequency in the range of 100 kHz to 1 MHz

- Minimal ESR due to low-loss copper electrodes and HF-suited backend

- Typ. ESR @ 25 °C, 1 MHz\*: 3 ... 45 mΩ

- Typ. ESL\*: 2 ... 4 nH

- No limitation of dV/dt

- Temperature decrease with rising frequency

Due to low losses at high temperature and high frequency, CeraLink can carry more current under these conditions

| Measurement condition                                                       | MKP film<br>capacitor  | MLCC class II<br>(BTO) | CeraLink   |

|-----------------------------------------------------------------------------|------------------------|------------------------|------------|

| Typical capacitance density  @ DC link voltage, 20 V <sub>RMS</sub> , 25 °C | 0.7 μF/cm <sup>3</sup> | 2.5 μF/cm <sup>3</sup> | 4.9 μF/cm³ |

| Typical current rating per capacitance @ 100 kHz, 105 °C                    | < 1 Α/μF               | < 4.5 A/µF             | 11 Α/μF    |

\*varies with series and voltage class

# **Attracting Tomorrow**

# **Technology Insights**

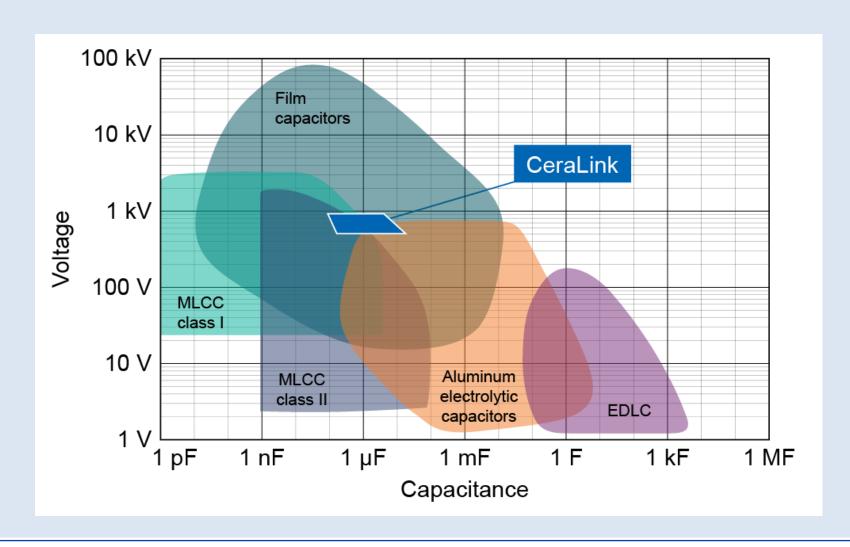

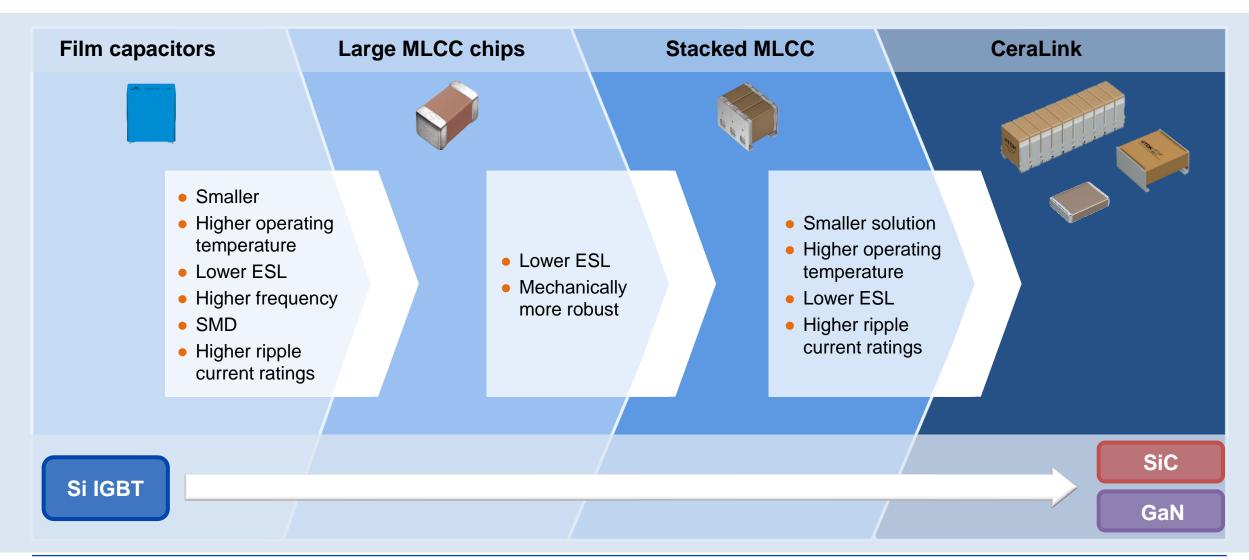

## Capacitor technology landscape

# **Technology guideline**

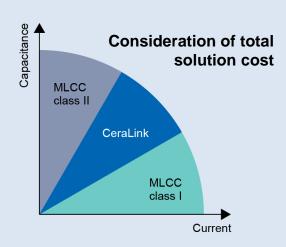

# Positioning CeraLink in capacitor landscape

### **General**

| Capacitance at voltage                     | Film<br>capacitor | MLCC<br>class II | CeraLink |

|--------------------------------------------|-------------------|------------------|----------|

| Nom. / rated capacitance                   | 100%              | 100%             | 100%     |

| No bias<br>voltage<br>0.5 V <sub>RMS</sub> | 100%              | 100%             | 35%      |

| DC link<br>voltage<br>0.5 V <sub>RMS</sub> | 100%              | 35%              | 60%      |

| DC link<br>voltage<br>20 V <sub>RMS</sub>  | 100%              | 35%              | 100%     |

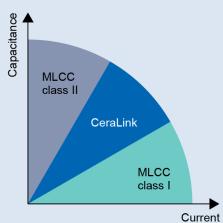

### **Ceramic landscape**

| Special requirements | MLCC<br>class I | MLCC<br>class II | CeraLink |

|----------------------|-----------------|------------------|----------|

| Resonance, stable C  | ✓               | ×                | ×        |

| T >125 °C            | ✓               | X8R / custom     | ✓        |

| V >630 V             | ✓               | Limited offer    | <b>✓</b> |

| AC                   | ✓               | ✓                | ×        |

| Current              | ••••            | •••••            | •••••    |

# Consideration of total solution cost

### CeraLink LP versus MLCC class II

Capacitance @ 400 V + 20 V ripple

Similar like

Ripple current @ 100 kHz & 85 °C

Similar like

Added value of CeraLink LP series

- Less PCB space

- Higher temperature

- Low ESL

Stacked MLCC based on case size 2220

# CeraLink's special behaviour... (1)

### ... positive bias behaviour

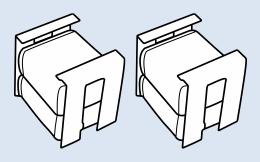

CeraLink features a non-linear capacitance behavior, i.e. the capacitance strongly depends on external parameters such as the applied DC bias voltage or the temperature. It is important to note that CeraLink is designed to have its capacitance maximum under operating conditions, i.e. under a DC bias (constant operating voltage) and with a superimposed ripple amplitude.

More to this in the CeraLink Technical Guide

# CeraLink's special behaviour... (2)

### ... at high temperatures

- Operating temperature up to +150 °C

- Low ESR

- Low leakage current

- No thermal runaway

- Superb heat transport capabilities to PCB due to copper-invar-copper (CIC) lead frames\*

- High ripple currents of up to 11 A/μF

- Generally low self-heating AND self-heating supports CeraLink to come to temperature for good performance

Temperature sensor Chip Lead frame

<sup>\*</sup>used for CeraLink® LP, FA and SP series

## CeraLink's special behaviour... (3)

### ... at high frequencies

- Perfect for frequencies up to 1 MHz

- No limitation of dV/dt

- Minimal ESR at high temperatures due to low-loss copper electrodes and HF suited backend

- Typ. ESL\* 2 to 4 nH

- → Perfect as snubber or in filter applications

\*varies with series and voltage class

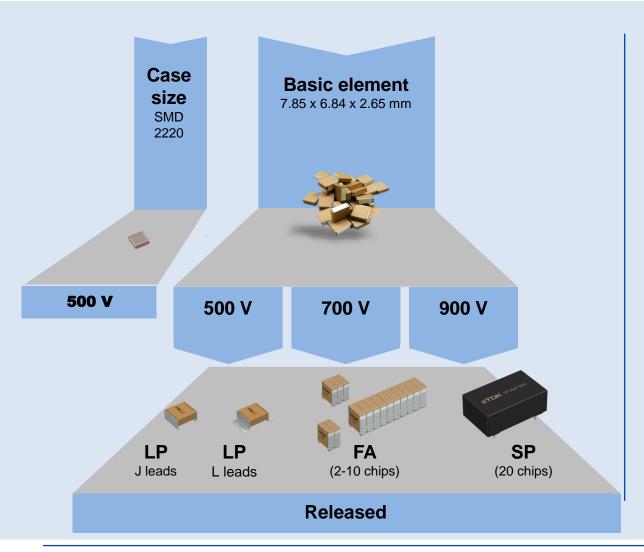

# **CeraLink product portfolio**

| Series                                           | Rated voltage          |            |                  |  |  |

|--------------------------------------------------|------------------------|------------|------------------|--|--|

| Series                                           | 500 V                  | 700 V      | 900 V            |  |  |

| Low profile LP (L /J leads)                      | 1 μF                   | 0.5 μF     | 0.25 μF          |  |  |

| Flex assembly FA2 / FA3                          | 2/3 μF                 | 1 / 1.5 μF | 0.5 / 0.75<br>μF |  |  |

| Flex assembly FA10                               | 10 μF                  | 5 μF       | 2.5 μF           |  |  |

| Solder pin SP                                    | 20 μF                  | 10 μF      | 5 μF             |  |  |

| 2220 series SMD 2220 Standard + Soft Termination | 0.25 μF @<br>h: 1.4 mm |            | Coming soon      |  |  |

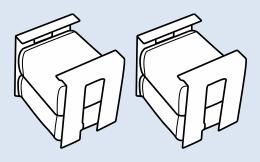

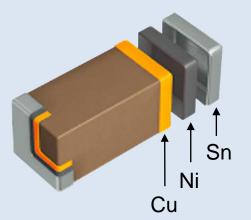

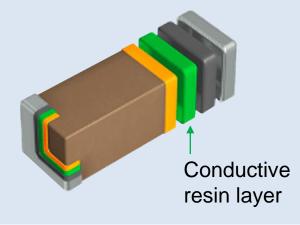

### CeraLink SMD 2220 series

- Optimized for capacitance density (MLCC design)

- Termination

- ¬ Standard: Cu cap with Ni/Sn galvanics

- Soft electrode: additional conductive resin layer absorbing mechanical stress

### Regular terminal product

**Soft termination**

- 500 V component with 1.4 mm height

- $\neg$  C<sub>nom, typ</sub>: 250 nF

- $\neg$  I<sub>RMS</sub> @100 kHz and 85 °C: 5 A

# **CeraLink product outlook**

### The chip size components

#### CeraLink SMD 2220 500 V

h: 1.4 mm

C<sub>nom, typ</sub>: 250 nF

Released

#### CeraLink SMD 2220

with maximum capacitance due to higher height

500 V component

900 V component

#### CeraLink SMD 1210 500 V

with maximum capacitance due to higher height

500 V component

900 V component

All case sizes in both termination available: Cu cap with Ni/Sn galvanics, soft electrode with additional conductive resin

... other voltage classes

# **Attracting Tomorrow**

# **Application Insights**

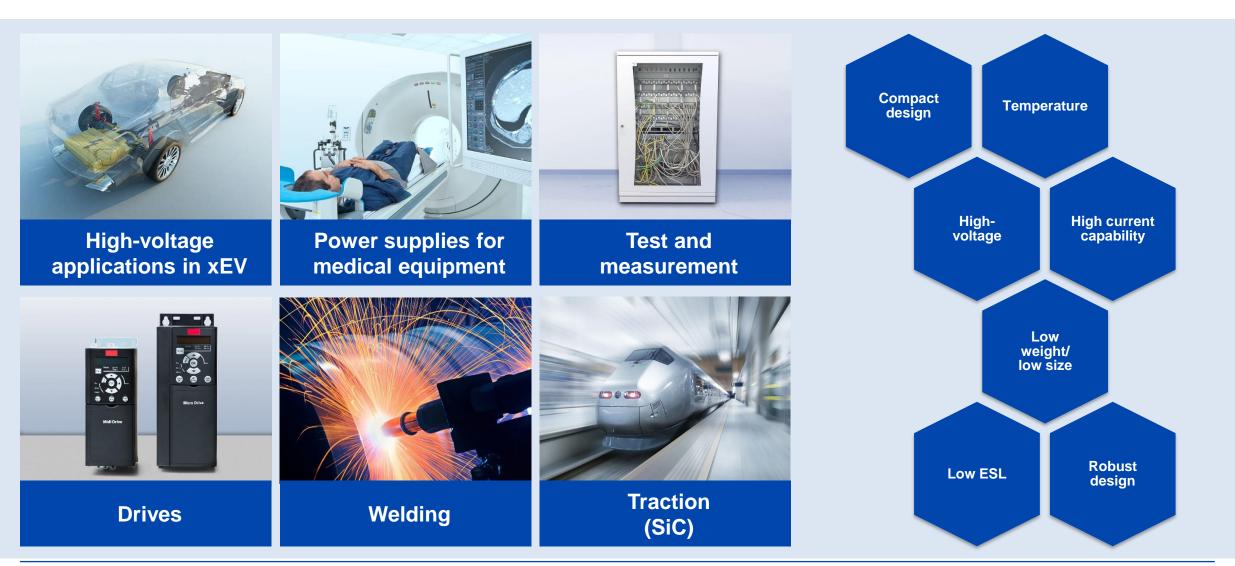

# **CeraLink target applications**

### Principle circuit diagram of function of capacitors in e.g. motor drives

#### **Main function**

- Snubber capacitor

- Filter capacitor

- Flying capacitor

- DC-link capacitor

#### Scope

- High power density

- High efficiency

- High temperature

DC link

Snubber

Output filter

# CeraLink®: Ideal for demanding applications (examples)

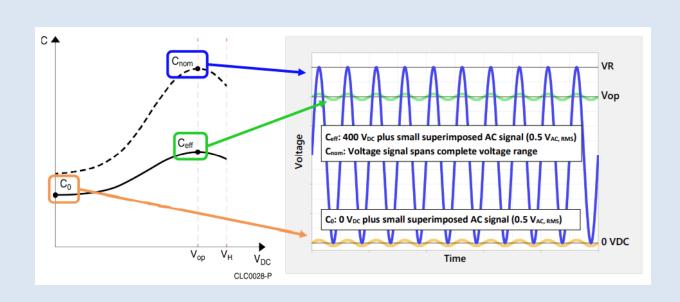

### CeraLink as DC link

| Series             | Maximum voltage ratings |               | Footures       |                                         |  |

|--------------------|-------------------------|---------------|----------------|-----------------------------------------|--|

| Series             | 650 V                   | 1000 V        | 1300 V         | Features                                |  |

| Flex Assembly FA10 | 10 μF / 500 V           | 5 μF / 700 V  | 2.5 μF / 900 V | The capacitance characteristic and low  |  |

| Solder Pin<br>SP   | 20 μF / 500 V           | 10 μF / 700 V | 5 μF / 900 V   | ESR of CeraLink avoid a thermal runaway |  |

In parallel connection, higher temperature leads to:

- Lower capacitance

- Higher impedance

- Lowest current through the <u>hottest</u> capacitor → self-regulating properties

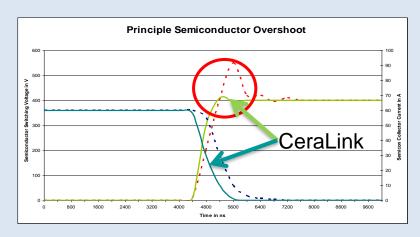

### 1 per half bridge - mounted close to the semiconductor

| Series                      | Maximum voltage ratings        |                              | Features               |                                                                                              |

|-----------------------------|--------------------------------|------------------------------|------------------------|----------------------------------------------------------------------------------------------|

| Series                      | 650 V                          | 1000 V                       | 1300 V                 | realures                                                                                     |

| Low Profile LP (L /J leads) | 1 μF / 500 V                   | 0.5 μF / 700 V               | 0.25 μF / 900 V        | <ul> <li>Low ESL (typ. 3 nH)</li> </ul>                                                      |

| Flex Assembly FA2 / FA3     | 2/3 μF / 500 V                 | 1/1.5 μF / 700 V             | 0.5/0.75 μF /<br>900 V | <ul> <li>Low losses at high frequencies and<br/>high temperatures (up to +150 °C)</li> </ul> |

| SMD 2220 - New              | 0.25 μF / 500 V<br>@ h: 1.4 mm | Coming soon in new h: 1.9 mm |                        | No limitation of dV/dt                                                                       |

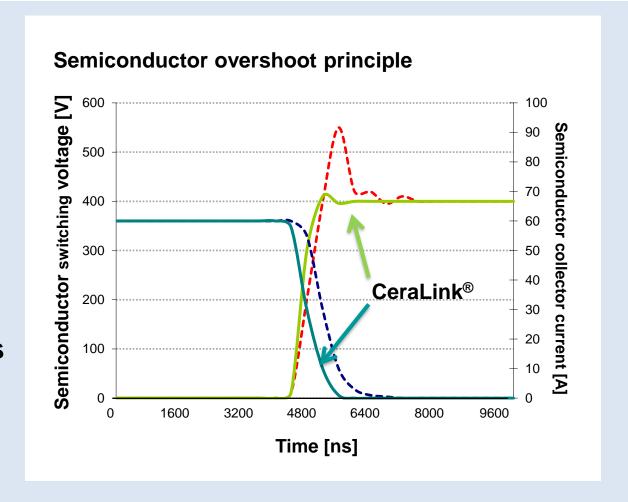

Over-voltages or over-shoots occur when switching off a Semiconductor.

This will cause an overvoltage according the formula (see left)

The low inductance of the CeraLink enables a faster switching of the semiconductor resulting in lower switching losses, enabling a reduction of switching losses of up to 40%!

$$V = -L \cdot \frac{di}{dt}$$

# CeraLink: Ideal for demanding applications Key facts

#### **Target applications**

#### **Automotive**

- OBC

- DC/DC

- Auxiliary inverters for xEV (HV compressor, HV pump, HV heater)

#### Industry

- Drives

- Energy storage systems

- Power converter

- Solar inverters

- Power supplies like UPS, isolated power supply

- SiC Power Modules

- Suitable for HV designs like 400 V/800 V

- Increasing capacitance with DC bias and best in class capacitance density at operating point (V<sub>op</sub> + T<sub>op</sub>)

- Supports miniaturization with low inductive design

#### **Basic facts**

Qualification based on AECQ-200

Manufacturing site in EU (Deutschlandsberg, AT)

Quality management system according to IATF 16949:2016

Soldering Method: Reflow

#### **Unique features**

Innovative anti-ferroelectric ceramic material (positive bias behaviour)

High cooling efficiency due to high thermal conductivity

Good self-regulating properties

### Resulting advantages

High capacitance density

High current capability

Low ESL (typ. 3 nH)

Low losses at high frequencies and high temperatures (up to +150 °C)

No limitation in dV/dt

→ Ideal as snubber, filter cap and flying capacitor for SiC and GaN applications

www.tdk-electronics.tdk.com